Čovek sa društvene mreže Twitter (X), inženjer koji se potpisuje kao @MajmudarAdam podelio je na svom profilu svoje iskustvo o tome kako je dizajnirao GPU „od nule i bez prethodnog iskustva“. Kao i sa njegovim prethodnim projektom dizajniranja CPU-a od nule, njemu je za ovaj poduhvat bilo potrebno samo dve nedelje.

U svom nizu objava, on nas vodi kroz proces dizajna GPU-a korak po korak i priznaje da je dizajniranje bilo mnogo teži zadatak nego što je očekivao. Da bude jasno, trenutni zaključak projekta je čip u Verilog-u koji je konačno prošao kroz OpenLane EDA softver radi provere. Međutim, GPU će biti poslat na izradu preko Tiny Tapeout 7, pa bi trebalo da postane stvaran čip u narednim mesecima.

Iako je ovaj projekat predstavljen kao onaj koji kreće od nule, bilo je potrebno puno proučavanja i razmišljanja čak i pre nego što je prvi korak bio preduzet. Prošli put zabrinutost inženjera bila je to da će GPU-ovi biti relativno teško polje za proučavanje, zbog dominacije vlasničke tehnologije, što se pokazalo kao tačno.

Twitter (X) profil: @MajmudarAdam

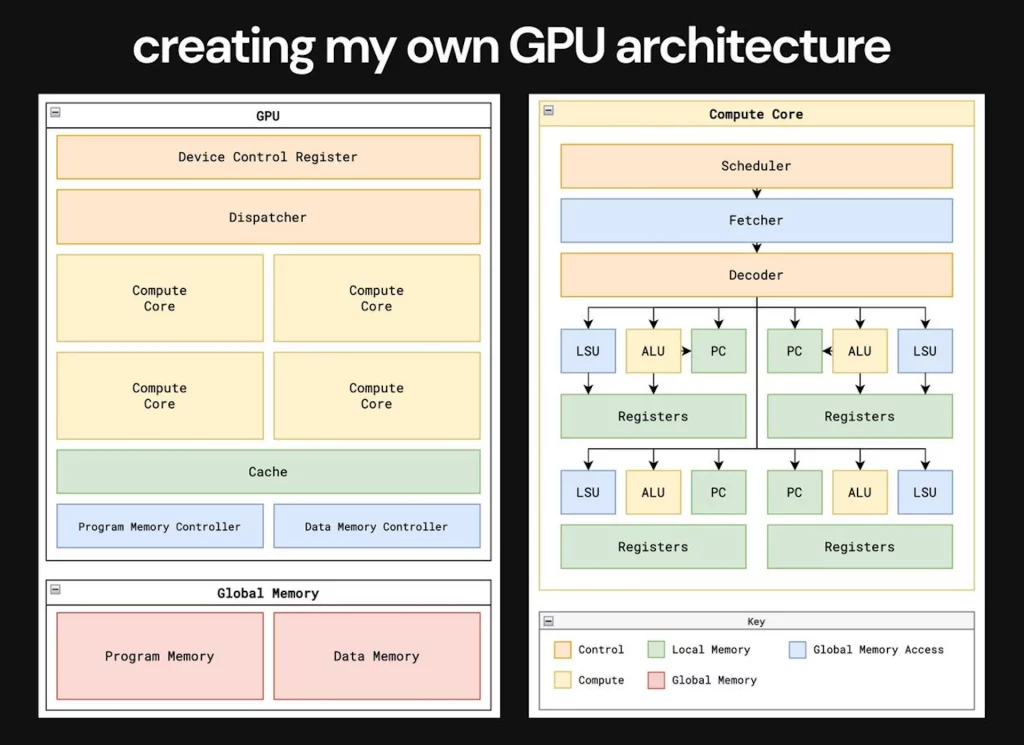

Twitter (X) profil: @MajmudarAdamKroz nekoliko iteracija arhitekture iz njegovog niza objava, ovaj inženjer odlučio je da se fokusira na mogućnosti paralelnog računarstva opšte namene (GPGPU). On je, tako, prilagodio svoj set instrukcija (ISA), koji ima samo 11 instrukcija, kako bi postigao ovaj cilj. Zatim je napisao dve matematičke matrice koje treba da rade na ovom GPU čipu. Ova jezgra za dodavanje i množenje matrica trebalo bi da pokažu ključnu funkcionalnost GPU-a i pruže dokaze o njegovoj korisnoj primeni u grafici i zadacima mašinskog učenja.

Do sada je bilo relativno lako za inženjera, ali izgradnja GPU-a u Verilogu donela jem kako tvrdi, mnogo problema. Saveti (poznatog) Džordža Hoca pomogli su mu da prevaziđe jednu od svojih prvih prepreka u vezi sa memorijom i implementacijom „warp“ planera. Međutim, treće ispravljanje njegovog koda je rešilo problem. Nakon nekoliko neodređenih prepravki, dokaz u vidu videa koji prikazuje rad jezgra za dodavanje matrica i njegovo validiranje, podeljen je u nizu tvitova.

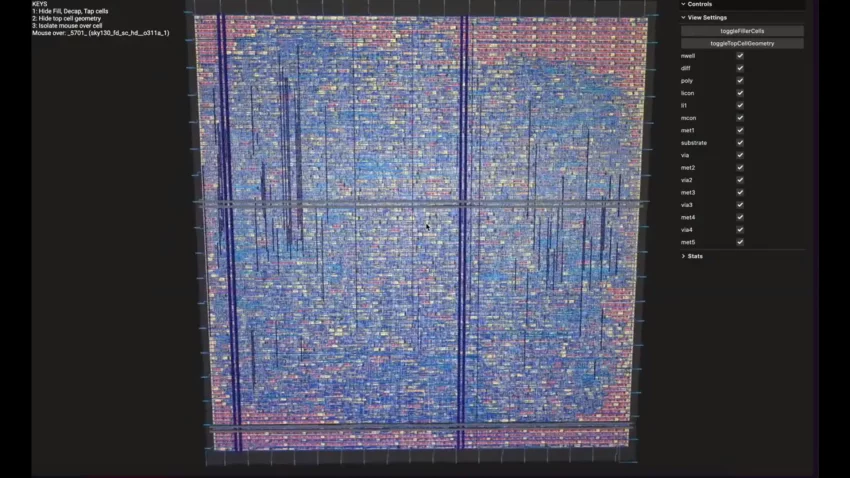

Na kraju, završen Verilog dizajn je prošao kroz OpenLane EDA, ciljajući na Skywater 130 nm proces izrade čipa (za Tiny Tapeout). Ipak, tada su se ponovo pojavili neki problemi koje je bilo potrebno rešiti. Konkretno, inženjer objašnjava da su neke provere dizajna (DRC) bile neuspešne i zahtevale su ponovni rad.

Nakon dvonedeljnog napora, inženjer je uživao igrajući se sa kul 3D vizualizacijom svog GPU dizajna. To će morati da bude dovoljno dok TT7 ne vrati silicijum učesnicima, a ako želite da pročitate više o ovom ručno pravljenom GPU čipu, možete da se informišete na pomenutom Twitter profilu.

Nema komentara 😞

Trenutno nema komentara vezanih za ovu vest. Priključi se diskusiji na Benchmark forumu i budi prvi koje će ostaviti komentar na ovaj članak!

Pridruži se diskusiji