Novi kompjuterski sistem će biti osnova budućih misija sa ljudima i bez ljudi, uključujući one na Mesec i Mars, a novi procesor će se razvijati u okvirima trogodišnjeg ugovora vrednog 50 miliona dolara koji je NASA potpisala sa kompanijama SiFive i Microchip. Novi CPU će koristiti RISC-V arhitekturu i menjaće vremešni PowerPC BAE RAD750.

Pre nego što postane zbunjujuća praksa menjanja procesora na dvadeset godina, potrebno je da razumemo da se ovi procesori koriste u vrlo specifičnom okruženju i obavljaju vrlo specifične poslove. Tako je pomenuti BAE RAD750 bio više nego dovoljan za kompleksne kalkulacije na različitim svemirskim misijama.

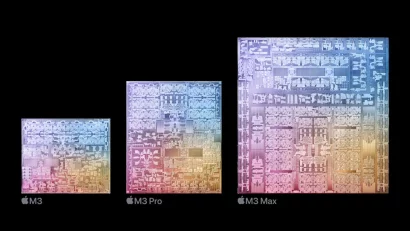

100 puta bolje performanse

Zbog toga se planira da se novi procesor koristi u narednim dekadama. SiFive tvrdi da će 12-jezgarni procesor koji prave u saradnji sa kompanijom Microchip omogućiti stostruko bolje performanse u odnosu na aktuelni procesor, nudeći pritom superiornu energetsku efikasnost zahvaljujući svojoj sposobnosti da isključi različite delove čipa kada se ne koriste. Ovo je posebno važno za nove generacije autonomnih rovera, obradu slika i snimaka, svemirskih letova, navođenja i komunikacija van Zemljine atmosfere i orbite.

Novi HPSC procesor će imati osam SiFive AI/ML optimizovanih X280 jezgara za vektorsku obradu pored četiri RISC-V CPU jezgra opšte namene. X280 je RISC-V CPU jezgro sa naprednim vektorskim matematičkim ekstenzijama.

SiFive tvrdi da vektorska unapređenja omogućavaju dizajneru čipova da postigne šest puta veću performanse od standardnih RISC-V vektorskih instrukcija, uz održavanje potrošnje platforme na niskom nivou.

Sa druge strane, pored performansi, čipovi koji putuju kroz svemir moraju da izdrže teške uslove rada. Nešto od toga dolazi iz arhitekture; nešto od toga potiče od samog dizajna čipa, a nešto dolazi iz procesa.

RISC-V

RISC-V je arhitektura koja je privukla značajnu pažnju i stotine miliona dolara investicija u poslednjih nekoliko godina, delimično zahvaljujući svojoj otvorenoj, besplatnoj i laganoj prirodi. Osnovna arhitektura, kao klasičan RISC dizajn, sadrži manje od 50 instrukcija na koje se mogu dodati i zvanične i ekstenzije trećih strana, što donosi više instrukcija CPU jezgru, kako bi odgovarao njegovim operativnim zahtevima.

Na primer, ako ne želite matematičko ubrzanje sa pomičnim zarezom, možete se držati celobrojne baze i ekstenzija. Ali ako želite FPU, podršku za atomske instrukcije i druge funkcije, potrebno je da implementirate ta definisana proširenja u CPU jezgra.

Iako sada znamo osnovnu CPU arhitekturu iza NASA HPSC procesora, moramo sačekati da vidimo kako će dizajn na kraju biti implementiran, kao koje očvršćavanje zračenjem će se koristiti, i bilo koji drugi specijalizovani tretman koji zahtevaju poluprovodnici u svemiru.

Jedan od razloga zašto je NASA iskoristila Microchip za razvoj HPSC procesora je taj što ova kompanija reklamira nekoliko čipova ojačanih radijacijom. Dakle, SiFive obezbeđuje IP CPU-a, dok Microchip postavlja jezgra na odgovarajuću podlogu koja može preživeti u svemiru, sa potrebnim provodnicima i eto – RISC-V ide u svemir.

NASA posle više od 20 godina unapređuje hardver svog računara za navigaciju kroz svemir

Osmojezgarni SiFive RISC-V CPU će zameniti vremešni PowerPC BAE RAD750 koji je imao više letova nego bilo koji astronaut i koji se nalazi u Curiosity i Perseverance roverima, kao i u James Web teleskopu.